SPECIAL REPORT

001.3072068 CSIR NIPR PERS 227

PERS 227 FEASIBILITY STUDY OF TIME-SHARING ON A MINI-COMPUTER

NATIONAL INSTITUTE FOR PERSONNEL RESEARCH COUNCIL FOR SCIENTIFIC AND INDUSTRIAL RESEARCH

CSIR Special Report PERS 227 (pp. 1 - 91) UDC 681.322.063.4:681.322.063.31/.32 Johannesburg, Republic of South Africa, July 1975

PBC 1009

SPEC

HSRC Library and Information Service

RGN-Biblioteek en Inligtingsdiens

## DATE DUE - VERVALDATUM

| -      |     |

|--------|-----|

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        | 1 1 |

|        |     |

|        |     |

| PERS   |     |

| רבתם ו | l ( |

|        | 1 1 |

|        | 1   |

|        | 1   |

|        |     |

|        |     |

|        |     |

|        |     |

|        | (   |

|        |     |

|        | 1   |

|        |     |

|        |     |

|        |     |

|        |     |

|        | ]   |

|        |     |

|        | 1   |

|        |     |

|        |     |

|        | 1   |

|        | )   |

|        | 1 8 |

|        |     |

|        |     |

| 1      |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        | 1 2 |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

|        |     |

NATIONAL INSTITUTE FOR PERSONNEL RESEARCH COUNCIL FOR SCIENTIFIC AND INDUSTRIAL RESEARCH

CSIR Special Report PERS 227 (pp. 1-91) UDC 681.322.063.4:681.322.063.31/.32 Johannesburg, Republic of South Africa, July 1975

ISBN 0 7988 0740 7 CSIR Special Report PERS 227

Published by

National Institute for Personnel Research Council for <sup>5</sup>cientific and Industrial Research P.C. Box 10319 Johannesburg 2000 Republic of South Africa 1975

Printed in the Republic of South Africa by National Institute for Personnel Research

#### SUMMARY

At the time when the purchase of a computer for data acquisition and control of experiments was under consideration, a time-sharing system seemed to be indicated to handle the heavy work load expected, but there was some doubt about the feasibility of operating such a system on a mini-computer in the NIPR environment. To avoid the possibility of purchasing equipment which might not prove adequate, the suppliers were asked to lend the NIPR those items which were specifically required for time-sharing so that a feasibility study could be carried out.

The feasibility of the system was determined by experience with it in real-time data collection in on-going projects, and by experiments in which the effects of time-sharing were measured during crucial operations.

The results of the study showed that the system performs adequately and that it satisfies the needs of researchers. On the Varian minicomputer the VORTEX operating system, despite its large core overheads, provides an effective time-sharing system that enables real-time programs to be run together with program development and testing. The terminals provided gave adequate control from remotely situated laboratories.

The study showed that time-sharing real-time data collection is feasible in the NIPR environment and therefore it is recommended that the loaned equipment be purchased. This project was directed by Mr D.J.M. Vorster, Director of the National Institute for Personnel Research and was carried out as part of the activities of the Automation and Computer Services Division. Special thanks are due to Mrs F. Mekhoe and Mrs N.J. Twala for typing the text and to Mr A.D. Molatedi for drewing the grephs.

# <u>Page</u>

| 0 | INTRODUCTION                                         | 1  |

|---|------------------------------------------------------|----|

|   | Structure of the Report                              | 2  |

| 1 | PURPOSES FOR WHICH THE NIPR REQUIRED A MINI-COMPUTER | 3  |

|   | 1.1 Neuropsychology Division                         | 3  |

|   | 1.2 Temperament and Personality Division             | 5  |

|   | 1.3 Psychometrics Division                           | 6  |

| 2 | EXPECTED USAGE OF THE MINI-COMPUTER                  | 7  |

| 3 | PROS AND CONS OF PURCHASING A TIME-SHARING MINI-     |    |

|   | COMPUTER                                             | 9  |

| 4 | PROPOSAL TO UNDERTAKE A FEASIBILITY STUDY            | 12 |

| 5 | HARDWARE AND SOFTWARE USED FOR THE FEASIBILITY STUDY | 13 |

|   | 5.1 Configuration Chosen                             | 13 |

|   | 5.2 Computing Facilities                             | 13 |

|   | 5.3 Camac Capabilities                               | 14 |

|   | 5.4 Resource Allocation                              | 14 |

| 6 | DETAILED DESCRIPTION OF RELEVANT HARDWARE            | 16 |

|   | AND ITS OPERATION                                    |    |

|   | 6.l Varian 73 Interrupt and I/O Options              | 16 |

|   | 6.2 Camac System                                     | 18 |

|   | 6.2.1 Introduction of the Camac Concept              | 18 |

|   | The Camac Control Hierarchy                          | 19 |

|   | The Camac LAM Concept                                | 19 |

|   | 6.2.2 The Camac System at the NIPR                   | 21 |

|   | Introduction                                         | 21 |

|   | Block Transfer of Data                               | 22 |

| 7 | RELEVANT SOFTWARE                                    | 24 |

|   | 7.1 The Vortex Operating System                      | 24 |

|   | 7.2 Camac Programming under Vortex                   | 25 |

|   | 7.3 Data Collection                                  | 26 |

| 8 | VERIFICATION OF DATA-SPOOLING CAPACITY               | 27 |

|   | 8.1 Data Transfer Rate                               | 27 |

|   | Conclusions                                          | 28 |

|   | 8.2 The Effects of Conflict Between Programs         |    |

|   | for Access to the Disk                               | 29 |

|   | 8.3 Effects of Conflicting Priorities                | 29 |

|   | 8.4 Comparison of Actual with Theoretical Timing     |    |

|   | Calculations                                         | 30 |

|   | 8.5 Summary                                          | 30 |

| 9 | VERIFI | CATION O | F THE TIME-SHARING CAPABILITIES OF THE |    |

|---|--------|----------|----------------------------------------|----|

|   | SYSTEM | 1        |                                        | 31 |

|   | 9.1    | Introdu  | ction                                  | 31 |

|   | 9.2    | Termino  | logy                                   | 31 |

|   | 9.3    | Experie  | nce with the System                    | 31 |

|   | 9.4    | Experim  | ents for Timing Interrupt-Driven       |    |

|   |        | Transfe  | rs of Control                          | 33 |

|   |        | 9.4.1    | Introduction and Background to the     |    |

|   |        |          | Timing Experiments                     | 33 |

|   |        | 9.4.2    | The Data Acquisition Process           | 33 |

|   |        |          | Block Transfer                         | 34 |

|   |        |          | . Normal Mode                          | 36 |

|   |        | 9.4.3    | Comparison of Camac Timer and Varian   |    |

|   |        |          | Timer Rates                            | 37 |

|   |        | 9.4.4    | The First Series of Experiments :      |    |

|   |        |          | Normal Mode, Command Timing            | 38 |

|   |        |          | Method and Measurements                | 38 |

|   |        |          | Résults                                | 42 |

|   |        | 9.4.5    | The Second Series of Experiments :     |    |

|   |        |          | Normal Mode, Continuous Timing         | 45 |

|   |        |          | Method and Measurements                | 45 |

|   |        |          | Constraints Necessary for Data         | i. |

|   |        |          | Integrity                              | 47 |

|   |        |          | Results with One Real-Time             |    |

|   |        |          | Program                                | 48 |

|   |        |          | Results with Two Real-Time             |    |

|   |        |          | Programs                               | 51 |

|   |        |          | The First Experiment                   | 51 |

|   |        |          | Comparison with Theoretical            |    |

|   |        |          | Upper Bounds                           | 51 |

|   |        |          | The Second Experiment                  | 52 |

|   |        |          | Conclusions                            | 53 |

|   |        |          | Program Design Guidelines              | 54 |

|   |        | 9.4.6    | Experiments with Block Transfer Using  |    |

|   |        |          | Continuous Timing                      | 55 |

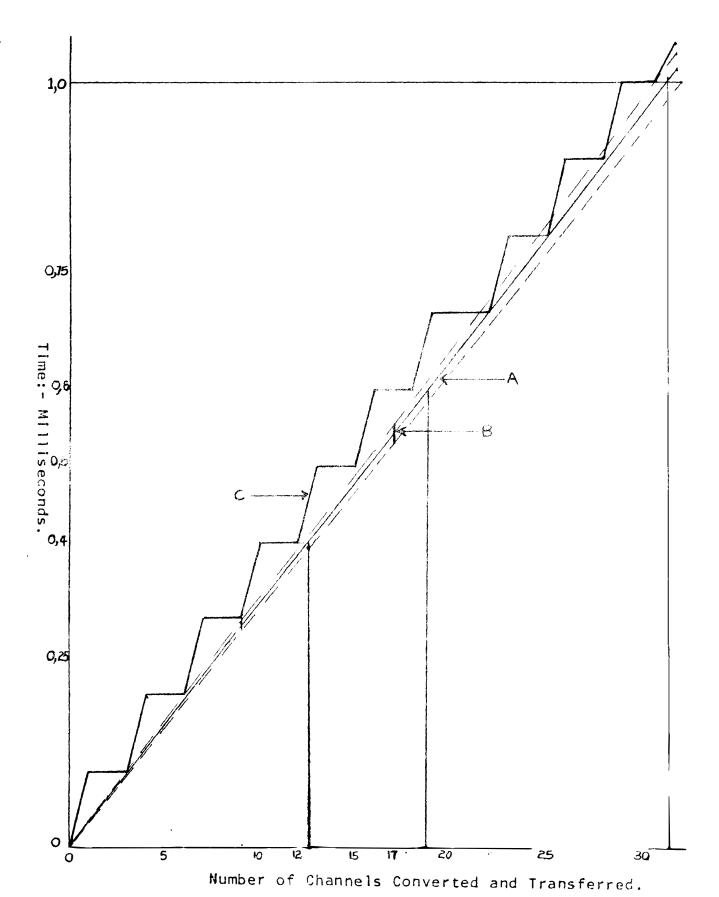

|   |        |          | Data Conversion Times                  | 56 |

|   |        | 9.4.7    | Timing of R.T.E. Functions             | 58 |

|   |        | 9.4.8    | Further Results of the Experiments     | 60 |

|   |        | 9.4.9    | Conclusions and Summary                | 61 |

| 10 | FURTHER ASPECTS OF THE FEASIBILITY STUDY      | 62 |

|----|-----------------------------------------------|----|

|    | 10.1 Simultaneous Use of Several Laboratories | 62 |

|    | 10.2 Amount of Main Memory Used               | 63 |

|    | 10.3 Printing Requirements                    | 66 |

| 11 | FINAL CONCLUSIONS AND RECOMMENDATION          | 67 |

# <u>APPENDICES</u>

| Al         | Computer Configuration                                                                           | 69 |

|------------|--------------------------------------------------------------------------------------------------|----|

| A2         | Common Symbols and Macros                                                                        | 73 |

| А3         | Example of a Program Segment for Initializing<br>the BIC and CAMAC in a Block Transfer Operation | 75 |

| A4         | Interrupt Assignments                                                                            | 76 |

| A5         | Camac Modules and Interface                                                                      | 78 |

| <b>A</b> 6 | NIPR Programming Conventions for the Camac                                                       |    |

|            | Equipment                                                                                        | 81 |

| A7         | Interrupt Handlang                                                                               | 85 |

| A8         | Glossary of Data Processing Terminology Used in                                                  |    |

|            | the Report                                                                                       | 88 |

# List of Tables

| <u>Table</u> | <u> </u>                                                                  | ag         |

|--------------|---------------------------------------------------------------------------|------------|

| 2.1          | Estimates of Time to Complete a Project by<br>Division                    | 7          |

| 2.2          | Estimates of Total Time Requirements                                      | 8          |

| 5.1          | Resource Requirements                                                     | 14         |

| 5.2          | Experiment Combinations                                                   | 15         |

| 8.1          | Disk and Tape Rates                                                       | <b>2</b> 8 |

| 9.1          | Comparison of Camac and Varian Timer Rates                                | 37         |

| 9.2          | Statistics from Experiments Using Normal Mode<br>and Timing on Command    | 42         |

| 9.3          | Statistics from Experiments Using Normal Mode<br>and Continuous Timing    | 48         |

| 9.4          | Statistics from Experiments Using Block Transfer<br>and Continuous Timing | 56         |

| 9.5          | Time to RESUME a Program                                                  | 59         |

| 10.1         | Input/Output Buffering Memory Requirements                                | 64         |

| 10.2         | Memory Requirements for Program Development<br>Facilities                 | 65         |

# 8

# List of Figures

# <u>Figure</u>

# Page

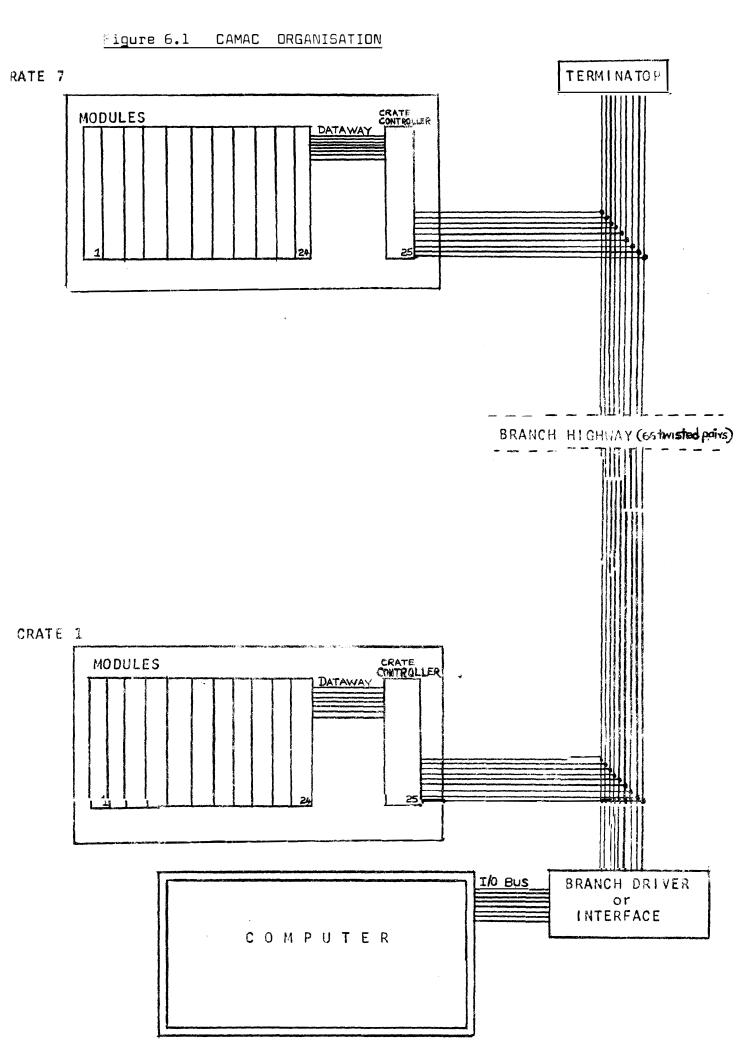

| 6.1          | Camac Organisation                                                      | 20          |

|--------------|-------------------------------------------------------------------------|-------------|

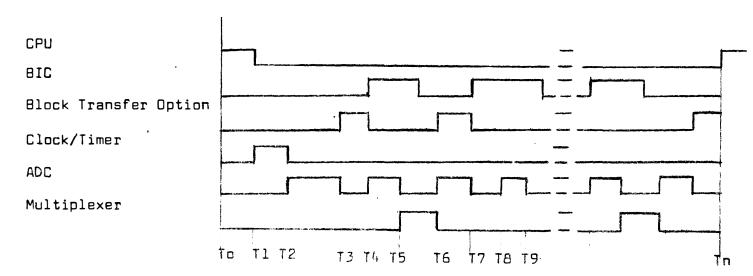

| 6.2          | Timing Chart for Block Transfer of Data                                 | 23          |

| 7.1          | Data Collection System                                                  | 26          |

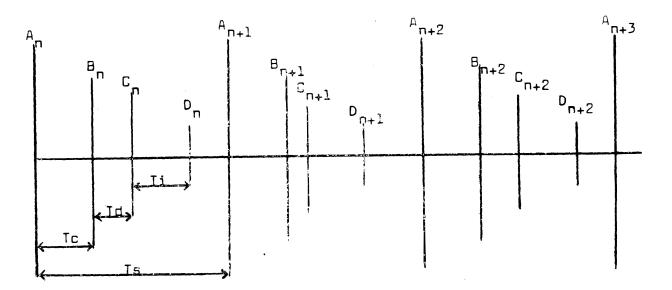

| 9.1          | Data Sampling Timing Chart for Block Transfer                           | 35          |

| 9.2          | Timing Chart for Data Sampling under Program<br>Control                 | 36          |

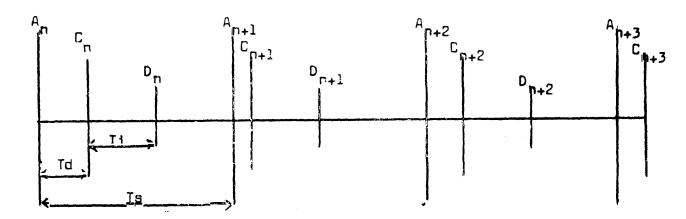

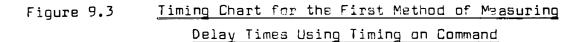

| 9.3          | Timing Chart for First Method Using Timing on<br>Command                | 40          |

| 9.3a         | Timing Chart Showing Entrainment of One Program<br>by Another           | 41          |

| 9.4          | Time-Sharing a Real-Time Program with Non-Real-<br>Time Programs        | 48 <b>a</b> |

|              | Time-Sharing two Real-Time Programs : Continuous<br>Timing, Normal Mode |             |

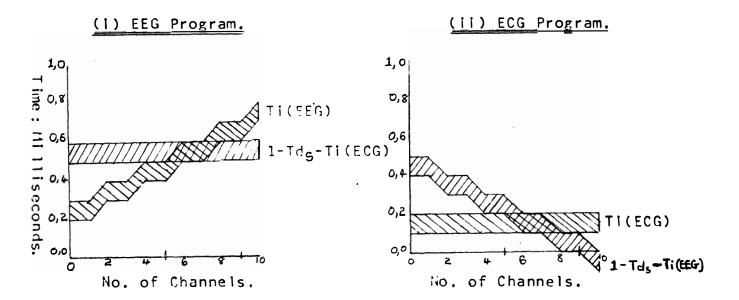

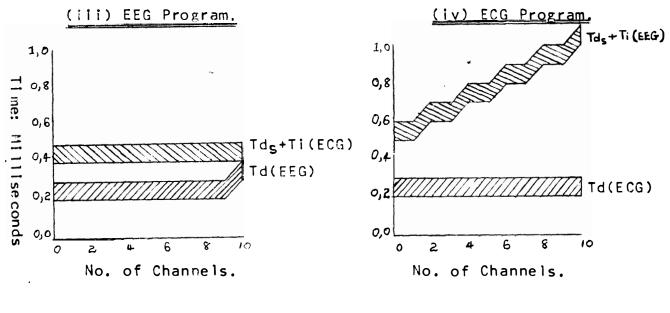

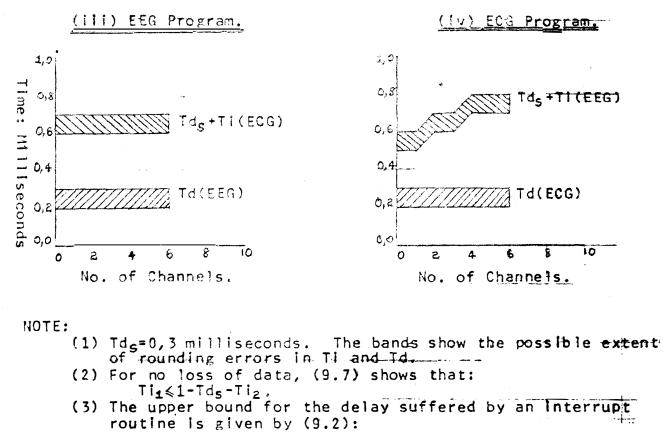

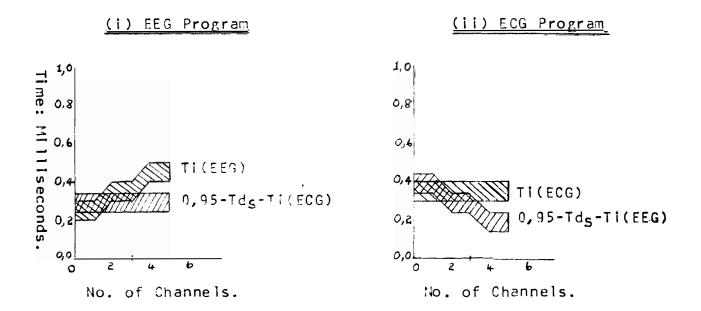

| 9.5 <b>a</b> | EEG Program - 1 to 10 Channels                                          | 50a         |

| 9.5b         | ECG Program - 1 Channel                                                 | 50b         |

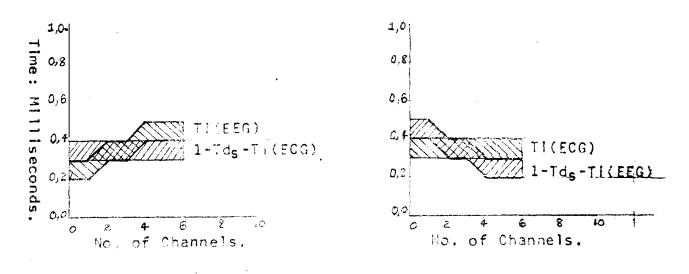

| 9 <b>.5c</b> | Comparison with Theoretical Upper Bounds                                | 50c         |

| 9.6 <b>a</b> | <u>EEG Program - 1 to 6 Channels; ECG Program -</u><br>5 Channels       | 50 <b>d</b> |

| 9.66         | Comparison with Theoretical Upper Bounds                                | 50e         |

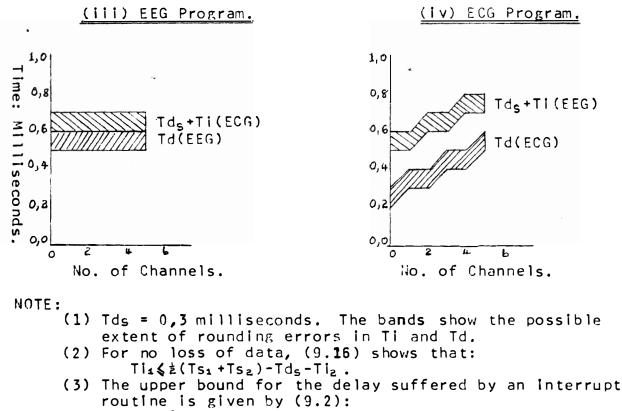

| 9 <b>.7a</b> | Sampling at Different Rates                                             | 51a         |

| 9.76         | Comparison with Theoretical Upper Bounds                                | 51ь         |

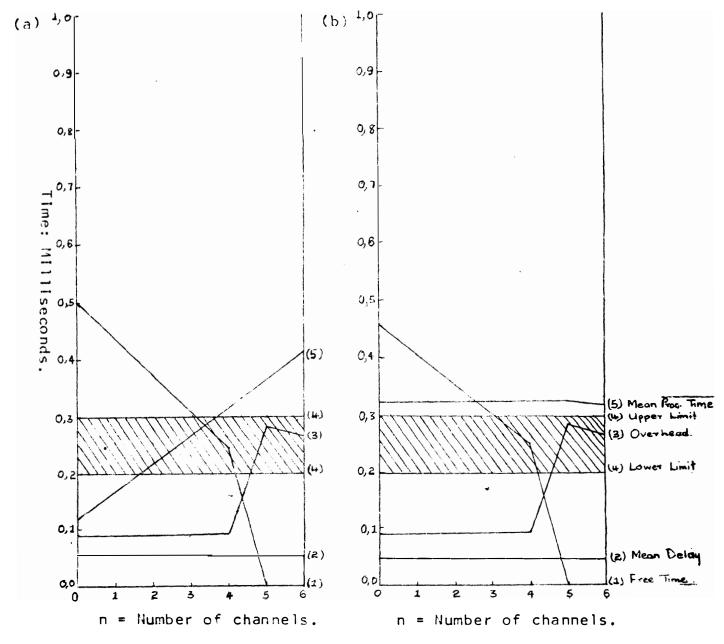

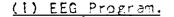

| 9.8          | Data Conversion Times with Block <b>Transfer</b>                        | 56a         |

#### Chapter O

#### Introduction\_

In the early 1970's it became apparent that several divisions of the NIPR required a mini-computer for their research. Ιn analysing their needs it was found that the various functions the computer would be called upon to perform fell into one of three broad classifications : data collection, data analysis, and experimental control. The most urgent requirement and the most demanding in terms of computer capability was the monitoring and sampling of various physiological functions such as the electroencephalograph. The data analysis the mini-computer would be expected to perform would be simple and undemanding in terms of scheduling; most analyses would be performed on a large digital computer. Experimental control, offering the new possibility of presenting stimuli to subjects in varying combinations of type, duration, intensity, at regular or random intervals etc. in a rigidly controlled and repeatable manner was also foreseen as a requirement in the near future.

The request for the services of a computer was identified to come from three divisions. The Neuropsychology Division required a computer urgently and expected to use it continuously. The Personality and Temperament Division, and the Psychometric Division had less urgent needs and expected to make use of the computer intermittently. The choice was seen to lie between the purchase of one dedicated machine to be followed later by a second 'general purpose mini-computer or a single larger machine capable of multiprogramming. The first alternative would prove to be more expensive in the long run, and would not provide the other divisions with adequate opportunities for development in the immediate future. Another consideration was that the acquisition of funds for the purchase of the second machine a year or so after the first might prove difficult. On the other hand there was considerable controversy over the feasibility of multi-programming on mini-computers. It was decided, therefore, to purchase a single machine and reach agreement with the supplier whereby the additional equipment required for multiprogramming would be loaned for a period during which a feasibility study would be carried out.

### The Structure of the Report

This report describes the circumstances leading up to the feasibility study, the equipment and software used, the results of the experiments performed and conclusions that can be drawn, Details of the functions which the various projects of the NIPR require of the mini-computer are presented in chapter 1. Chapter 2 indicates the expected usage, time-wise, of the mini-computer by the various projects. Chapter 3 examines the pros and cons of timesharing on a mini-computer and chapter 4 discusses the proposal to undertake a feasibility study to resolve the question. The basic configuration and the additional equipment required for the feasibility study is given in chepter 5, while chapters 6 and 7 give a detailed description of the relevant hardware and software. The verification of the feasibility study is discussed in terms of the data handling capacity of the system in chapter 8, the practicality of time-sharing real-time programs in chapter 9 and the results of experience with the system in chapter 10. The recommendations resulting from the study are presented in chapter 11.

#### Chapter 1\_

# The Purposes For Which the NIPR Required a Mini-Computer

#### 1.1 Requirements of the Neuropsychology Division

The principal work of the division involves monitoring neurophysiological functioning by amplifying and recording the electrical potentials generated by the nervous system. The electrical signals thus derived were (and to some extent, still are) evaluated by subjectively scanning the graphic output of the electroencephalograph or by making a multitude of measurements by hand, Some years ago a small special-purpose device, a Computer of Average Transients (CAT), was acquired by the Division. This device provided new analysis capabilities and relieved much of the manual work, but is limited in many respects when compared to a modern mini-computer. The increasing volume of work, the growing backlog of only partially analysed data and the need to apply sophisticated modern procedures created the need for computerised acquisition and conversion of data to a form suitable for further processing and enalysis and off-line storage. The analyses required included digital filtering, period-amplitude and Fourier analyses of the EEG, and the detection and measurement of characteristics of the evoked response.

The following is a precis of the requirements of the Division as set down in a memorandum by Dr. R.D. Griesel dated lith January 1972.

The techniques that a computer facility would extend or make possible included

(a) Evoked Response. Studies of brain potentials evoked in response to visual, auditory and/or somatic stimuli would particularly benefit from a computer controlled facility. Current experiments used manual methods of control, or special but limited hardware. The computer would also allow more accurate and detailed recording of the evoked response than the currently used special purpose Computer of Average Transients (CAT). Projects that would use this facility are 70/11, 64/42 and 63/3.

- (b) <u>Contingent Negative Variation</u>. A facility which the computer makes possible is the presentation of conditional stimuli, according to a programmable variable reinforcement schedule, for studying the amount of uncertainty people will tolerate for allowing the development of the electroencephalographic contingent negative variation. Projects that would use this facility are 64/3 and 70/11 as well as military and road safety projects.

- (c) <u>Complex Stimulation</u>. The computer would make feasible the presentation of complex visual stimuli on the visual display unit, or tachistoscopic presentation of visual stimuli, at automatically controlled programmable rates of information presentation. Projects that would use this facility are 70/11, 64/42, 63/3 and 64/3 as well as military and road safety projects.

- (d) <u>Controlled Stimulation</u>. The computer would be used to present stimuli only when certain conditions exist in the central nervous system. This facility would be incorporated in the programs providing the above functions.

# <u>Projects in the Neuropsychology Division Requiring the Use of a</u> <u>Mini-Computer</u>

- <u>Project 64/42</u> : Study of visual and auditory perception in different racial groups. The research aims at developing adeouate tests of visual and auditory functioning to allow a comparative study of a White and Bantu groups.

- <u>Project 70/11</u> : EEG and intelligence. The research aims at investigating the validity of measures of central nervous activity (as measured by the electroencephalographic signals evoked by a stimulus) for predicting performance on intelligence tests. The greater objectivity of the psychophysiological measures and their relevance in certain theories regarding intellective functioning would make them the preferred method of assessing intelligence in a way unaffected by the cultural assumptions inherent in traditional intelligence tests.

- <u>Project 71/17</u> : EEG and psychomotor development. This project aims at documenting in terms of both electroencephalographic and psychomotor measures the rate of maturation of the normal Bantu child. The earlier studies of the NIPR concerning the effects of malnutritution on behaviour will be extended to assess the influence of infantile malnutrition on development as assessed in the above-mentioned way.

- <u>Project 63/3</u> : The EEG, behaviour and brain damage. Although one aspect of this study includes the provision of a clinical assessement of the degree of brain damage found in certain cases of behavioural aberration, the project allows the acquisition of normative data and the investigation of the relationship between these electrocerebral measures and behavioural and neurological assessments of the extent of brain damage.

- Project 64/3 : Normal behaviour and brain function. On the basis of certain theoretical considerations it is expected that electrocerebral measures, including the EEG measures of speed of reaction to a stimulus, will be predictive of an individual's temperament as assessed psychometrically.

- <u>Other Projects</u> : Some projects not forming part of the Division's general research programme but relevant here are the clinical electroencephalographic assessments performed from time to time and a fairly heavy commitment to outside bodies with regard both to similar clinical screening services and research into psychophysiological problems.

### 1.2 Requirements of the Temperament and Personality Division

The need of the Division for the use of a mini-computer was set out in the third report of the sub-committee for assessing future needs for D.P. equipment in 1971 and in a memorandum by Miss E. Spies dated 25th January 1973. The computer would be used for data recording of physiological responses, test item presentation and on-line computation. Specifically, in project 64/19, Measurement of Effort, a computer was required to enable reliable measurement and recording of the heart-rate and several variables with which it is associated. The mini-computer would also make it possible to control accurately the stimulation producing various conditions of mental load (usually choice reaction in experimental studies). Preliminary analysis of the data would also be done on the minicomputer.

#### 1.3 Requirements of the Psychometrics Division

The Psychometrics Division set out its proposed immediate and future real-time computing requirements in the third report of the subcommittee for assessing future needs of D.P. equipment at the NIPR in 1973 and in a memorandum by M.A. Coulter dated 25th January 1973. Project 64/7, Rate of Information Processing (RIP), required the computerised presentation of stimuli on a visual display unit to a subject at increasing rates and the computerised scoring of the testee's response. The test measures the speed at which a person can receive, evaluate and act on perceptual information. The test has been implemented and used as part of a selection battery for pupil pilots, but difficulties in administering and manually scoring the test have caused it to be dropped from use.

•Future needs of the division for real-time computing facilities concerned with test presentation were envisioned as the following :

- (a) the investigation of memory processes,

- (b) the temporal integration of visual information,

- (c) the attentional and selective aspects of information processing,

- (d) testing tailored to individual requirements, and

- (e) testing with feedback.

All these projects require a visual display terminal attached to a responsive computer with data storage and timing facilities.

Chapter 2 The Expected Usage of the Mini-Computer

A survey was carried out in early 1972 to assess the expected work load on the mini-computer. The estimates of the expected usage of the mini-computer were derived from a questionnaire that was completed by the divisions that expected to make use of the machine and other members of the NIPR with relevant experience. Although the estimates could only serve as rough guidelines, they were made by experienced people and definite conclusions could be drawn.

The course of an experiment requiring the use of a mini-computer was broken down into six stages and the six participants in the survey were asked for their estimates of the time needed to complete each stage. The results shown in Table 2.1 ranged from two to ten months. The total requirements for the research program of each division is given in Table 2.2. This estimate of two years to work through the current research program of the Institute made no allowance for the use of the machine for other purposes and assumed that there would be no delays in scheduling projects to use the computer. Two years was therefore a minimum estimate and the total time was thought to be more likely to be between three and four years.

Table 2.1 Estimates of Time to Complete a Project by Division

| Experimental phase                                                                                              | and a second | of days for a<br>ERGONOMICS | <u>project</u><br>PSYCHOMETRICS |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|

| <ol> <li>Setting up apparatus and getting<br/>it to work properly.</li> </ol>                                   | 60                                                                                                             | 30                          | 5                               |

| <ol> <li>Compilation and testing programs<br/>for controlling the experiment<br/>and recording data.</li> </ol> | 43                                                                                                             | •<br>5                      | 2                               |

| <ol> <li>Trial runs with live subjects and<br/>the complete setup.</li> </ol>                                   | 4                                                                                                              | 5                           | 3                               |

| 4. Production - conducting the<br>experiment                                                                    | 20                                                                                                             | 8                           | 22                              |

| <ol> <li>Compilation and testing programs<br/>for simple analyses.</li> </ol>                                   | 23                                                                                                             | 5                           | 1                               |

| 6. Analyses.                                                                                                    | 100                                                                                                            | 8                           | 1                               |

| Total ⊓umber of days                                                                                            | 250                                                                                                            | 61                          | 34                              |

| Delays : 5% computer down, 5%<br>apparatus down, 10% other.                                                     | 50                                                                                                             | 12                          | 7                               |

| TOTAL NUMBER OF DAYS                                                                                            | 300                                                                                                            | 73                          | 41                              |

| TOTAL NUMBER OF MONTHS                                                                                          | 10                                                                                                             | 4                           | 2                               |

Computer Time Requirements

| Psychometrics               | 5 months                      |

|-----------------------------|-------------------------------|

| Temperament and Personality | $4\frac{1}{2}$ months         |

| Neuropsychology             | 13 months                     |

| Total time for 7 projects   | 22½ months or approx. 2 years |

Note : In estimating divisional dedicated requirements, it was assumed that constructing experimental apparatus and getting it to work would require only intermittent access to the computer and the main part of this would be overlapped with work on other projects and that this would also apply to a lesser extent to the compilation and testing of programs and trial runs with live subjects. Average times were obtained by weighting estimates according to the experience of the estimator.

Subsequent experience has shown that the Ergonomics and Psychometrics experiments required more than twice the time originally estimated. Unfortunately, no comparable information is available for EEG experiments as yet.

Admitting the roughness of the estimates, the conclusion was nevertheless inescapable that there was too much work for a single computer to handle in serial fashion. As the urgent need to process the large volumes of data generated by EEG projects would tend to lock out the development of programs needed for the experiments of the two other divisions, an acute conflict over computer resources could be anticipated. It was therefore necessary to consider the simultaneous multiple use of the computer, or the acquisition of two machines.

### Chapter 3

# Pros and Cons of Purchasing a Time-Sharing Mini-Computer

The question whether time-sharing on a mini-computer is practical is the subject of some controversy and cannot be answered in general. The answer depends on the desired application, on the available technology and on the current "state of the art". At the time the question was being considered in late 1972, Uttal, an eminent authority, was arguing against the use of small computers in a time-sharing fashion in the laboratory (1).\*\*

The general arguments for time-sharing are that it allows more effective use to be made of the CPU and that it allows one computer to do the work of two or more. Arguments against time-sharing in the laboratory are the following :--

- (i) The computer cannot service more than one user requiring rapid response as the first user to be served will lock out all other users.

- (ii) Operating system overheads are relatively heavier on mini-computers because of limited hardware and instructions.

- (iii) The cost of additional peripheral equipment to support time-snaring may be greater than the cost of purchasing additional computers.

- (iv) A time-sharing system requires a large programming effort to implement.

At the time of the decision on a time-sharing system for data acquisition in the NIPR's laboratories there were several manufactures of mini-computers that offered time-sharing facilities as pert of the standard software for their machines. Thus the fourth argument fell away.

\*\* The controversy is still very much alive : In October 1973 an entire session of The Third National Conference on the Use of On-line Computers in Psychology held at St. Louis, Missouri was devoted to actual time-sharing and multiprogramming applications.<sup>(2)</sup> In May 1975, Datamation carried an article by B.K.P. Horn and P.H. Winston arguing that the end of time-sharing is in sight.<sup>(3)</sup> Mast of the mini-computers on the market had interrupt systems to allow rapid program switching with low software overheads. The actual data collecting routines were expected to be short and simple, so that the time taken to process an interrupt would be very short. The data rates required by the NIPR projects were not high in comparison to typical mini-computer processor speeds - the maximum being 16 channels of data to be sampled every millisecond - and it was estimated that the time to read the data at this rate and transfer it to off-line storage would require about half a millisecond in every millisecond of CPU time. Most projects required much lower sampling rates. Thus timing considerations were not expected to pose any problems and arguments (ii) and (iii) were not expected to apply in the NIPR environment.

The position was therefore that, if it could definitely be established that time-sharing was feasible in the NIPR situation, i.e. that the above arguments were valid, then the deciding factor would be the cost of a computer capable of time-sharing compared with that of two dedicated machines, or, more accurately, the cost/benefit ratio. It is not strictly possible to compare a time-shared system with a non-time-shared system with equivalent experimental control facilities since each system will have facilities that the other does not have. For example, the time-sharing machine will be the larger and will therefore allow program development to take place more rapidly and will allow larger analysis type programs to be run. Bearing this in mind, the costs of two configurations quoted to the NIPR in early 1972 were as follows. One system was a Varian, configured for time-sharing at a cost of R53,350 and the other was a non-time-sharing system costing R45,000, viz. a difference of R8,350. A second, smaller machine with 8k memory, a teletype, a clock, an analogue to digital converter and a casette tape for communication with the larger machine (which would also need a casette tape) would cost R14,700 which is about twice the additional cost of the time-sharing system. It was also known that the first extension to the system would be a display unit for portraying the parameters of EEG data on-line so that the recording apparatus can be kept in step with changing conditions in the experiment, To fit a display unit on the smaller machine would

- 10 -

cost R8700 for the screen and interface wheareas these additions would only cost R4500 in the Varian machine. In this case, the difference in cost would be R10,500 in favour of the time-sharing system. Anticipated later needs for other peripherals such as printers, plotters, and additional memory capacity for both machines tips the balance still further in favour of the single machine. On this rough basis, the advantage in cost appears to lie with the time-sharing system.

- Uttal W.R. Misuse, abuse, overuse and unuse of on-line computer facilities by psychologists.

Behav. Res. Meth. and Instru;, 1972, Vol 4 (2) pp 55-60.

- (2) Proceedings published in Behav. Res. Meth. and Instru; 1974, Vol 6 (2).

- (3) Horn B.K.P. and Winston P.H. Personal Computers. Datamation 1975, Vol. 21 (5).

### Chapter 4 Proposal to Undertake a Feasibility Study

The proposal to use a mini-computer in time-sharing mode to sample data from two or more experiments simultaneously appeared feasible on theoretical grounds as worked out from program specifications, Camac speeds, magnetic tape and disk data rates and CPU processing times. But, because the performance of a system in practical situations often presents problems unforeseen in theoretical studies, it was decided to undertake a feasibility study before actually purchasing a full system.

Five propositions were put forward to be tested, i.e. that :-

- (1) Computer participation in NIPR experiments could be adequately handled from terminals located in laboratories remote from the computer. In the case of EEG experiments, the terminal was to be equipped with a display unit a key board and graphic and hardcopy facilities. In the case of Personality and Temperament experiments and Psychometrics experiments the terminals were to be equipped with a teletype and a visual display unit with a keyboard respectively.

- (2) Two typical NIPR experiments could be run simultaneously.

- (3) The minimum amount of core memory required would be 20K or 24K. The VORTEX operating system was expected to take 6K, and the Fortran compiler 8K so that to run a Fortran compilation and one foreground, data gathering program would require more than 16K.

- (4) The disk and tape unit could handle the maximum data rates. for storage and spooling.

- (5) A teleprinter would suffice for the printing that was necessary.

### 5.1 Configuration chosen for the feasibility study.

The precise details of the equipment chosen for the feasibility study are given in appendix Al. The essential features of the system are as follows. The computer is a Varian V73 with hardware multiply/divide, 24K 16 bit words of memory, an operator's teletype, a disk, and a magnetic tape drive. The data logging facilities are catered for by a Borer Camac crete containing an analog to digital converter, a 16 channel multiplexer, two clock/timers, and two I/O registers. The remote terminals are equipped with : (1) a Tektronix display unit with graphic and hardcopy facilities, (2) a teletype, and (3) an Infoton teletype compatible display screen. Cables run to each terminal for connecting experimental apparatus directly to the Camac units. A small line printer was added to the system later.

## 5.2 Computing Facilities.

Typical instruction times in core memory range from 66C nanoseconds for loading a register to 6641 nanoseconds for a divide instruction. The computer and Camac have extensive interrupt facilities and the VCRTEX disk-based operating system which is being used to run all programs on the machine, supports multi-programming. These features provide for rapid task switching when an interrupt is received. With this configuration it is possible to run programs for two experiments simultaneously (providing the programs have no conflicting peripheral, Camac or memory requirements).

Standard software which includes Fortran and an assembler with high level macro support for peripheral I/O and file handling facilities, allows the computer to support all proposed program development. However, the computer does not have floating point hardware, and fixedpoint arithmetic is performed on 16 bit words, so only the simpler forms of data analysis are possible.

#### 5.3 Camac Capabilities

The Camac system interfaces the computer with the experiment : the Camac crate contains modules for reading analog signals, reading and writing digital data, controlling sampling times and connecting outside (experimental) events to the computer's interrupt system.

#### 5.4 <u>Resource Allocation</u>

The following tables show the hardware requirements of different classes of experiments (Table 5.1) and the consequent restraints this imposes on multiple operation (Table 5.2)

#### Tablé 5.1

Resource Reguirements.

| EXPERIMENT                 |                             |                   |                   | RES         | GURCE |              |              |             |             |                          |

|----------------------------|-----------------------------|-------------------|-------------------|-------------|-------|--------------|--------------|-------------|-------------|--------------------------|

|                            | GPU USE DURING<br>INTERRUPT | MAGNETIC DISK (D) | MAGNETIC TAPE (T) | MULTIPLEXER | ADC   | I/O REGISTER | I/O REGISTER | CLOCK/TIMER | CLOCK/TIMER | VARIAN INTERVAL<br>TIMER |

| •                          | Milli-<br>secs              |                   |                   |             |       |              |              |             |             |                          |

| EEG(1) - DATA SAMPLING     | 0,5                         | or T              | or D              | *           | *     |              |              | *           |             |                          |

| EEG(2) - EVOKED RESPONSE   | C,5                         | or T              | or D              | *           | *     | *            |              | *           |             |                          |

| EEG(3) - CAT DATA TRANSFER | 0,05                        | or T              | or D              |             |       | *            |              |             |             |                          |

| ECG – DATA SAMPLING        | 0,3                         | or T              | or D.             |             | *     |              |              | *           |             | *                        |

| RIP - DATA GATHERING       | 0,01                        | or T              | or D              |             |       |              | *            |             | *           |                          |

| TEST PRESENTATION          | 0,01                        | *                 |                   |             |       |              |              |             |             |                          |

Note

- (1) An asterisk indicates the module or resource is required for exclusive use of the particular experiment.

- (2) In principle, all experiments may log their data to disk or to tape.

- (3) The CPU times listed include system overheads, and are estimates that were used in planning the study.

Table 5.2

### EXPERIMENT COMBINATIONS.

| EEG(1) | EEG(1) |        | • ·    |     |     |      |

|--------|--------|--------|--------|-----|-----|------|

| EEG(2) | C      | EEG(2) |        |     |     |      |

| EEG(3) | Ρ      | P      | EEG(3) |     |     |      |

| ECG    | С      | C      | Р      | ECG |     | _    |

| RIP    | Р      | Р      | ٩      | Р   | RIP |      |

| TEST - | Р      | Ρ      | P      | P   | Р   | TEST |

Note :

- C indicates a conflict in resource requirements.

P indicates it is possible to run the two experiments together.

- (2) The table is derived from resource requirements given in Table 5.1. Some EEG type (1) experiments may require exclusive use of the disk and will therefore conflict with the Test Presentation experiments. Also it would be possible for an ECG experiment to share the ADC via the Multiplexer with EEG type (1) or (2) experiments provided they did not need more than 15 channels.

# <u>Chapter 6</u> <u>Detailed Description of Relevant Herdware and</u> Its Operation

This chapter describes those features of the system that are exploited by the experimental control programs. The instruction set of the Varian 73 is not discussed as it contains all the standard types of instructions (including hardware multiply and divide but no floating point instructions) and no unusual commands. The V73 interrupt system is described in the first part of this chapter, together with the BIC and PIM I/O options. The second part of the chapter describes the Camac system and the Camac modules that are being used by the NIPR.

### 6.1 Varian 73 Interrupt and I/O Options

The standard I/O instructions transfer one word of data to or from a peripheral device under CPU control, but there is the Buffer Interlace Controller (BIC) option which permits peripherals to transfer blocks of data directly to or from memory at rates up to 382.720 words per second by implementing a cycle-stealing direct memory access technique that allows the transfer of data to proceed in parallel with other processing.Cycle-stealing trap requests inhibit the processing of a stored program for only the memory cycle (i.e. 660 nanoseconds) required to transfer one word of data between memory and the peripheral.

Data transfer by the BIC is established under program control. The status of the BIC is tested and if it is not busy it is initialised. The selected peripheral devices are then initialised and the BIC is supplied with the initial and final addresses of a block in memory for the data. The BIC is then activated, the peripheral started and the BIC assumes control of the transfer of data, thus freeing the CPU for other processing. An example of the use of a BIC is given in the program segment shown in appendix A3. The Varian 73 includes an interrupt capability by which certain I/Odevices (and options such as memory protect), can, on a priority basis, request the computer to execute an instruction or series of instructions independently of the program in progress. Following an interrupt, the computer is directed to a memory address specified by the interrupting device where it fetches and executes the instruction (normally a jump-and-mark instruction) that results in the processing of a service routine. The computer returns to the original program though an appropriate jump instruction at the conclusion of the routine. This method of directly connecting an interrupt to the appropriate service routine eliminates the software overhead encountered in some other machines where the operating system has to periodically test whether a bit has been set in a special register. The requirements for implementing an interrupt handling routine under the VORTEX operating system are discussed in chapter 7.

Standard Varian peripheral controllers are normally not capable of generating an interrupt when they require attention because they cannot provide the necessary memory address. This capability is provided by the Priority Interrupt Module (PIM). A peripheral controller connected to a PIM directs an interrupt request to the PIM, which in turn implements the interrupt. Up to eight interrupt lines can be serviced by one PIM. Interrupt requests are stored and serviced in the order of their priority, which depends on how the connections to the PIM are made from the peripherals. The PIM has an 8-bit mask register which can be used to enable any or all selected eight interrupt lines. Appendix A4 gives the allocation of interrupts as the machine was configured in July 1975.

ø

#### 6.2 CAMAC System\_

#### 6.2.1 Introduction to the CAMAC Concept

The Camac concept arose out of the need in nuclear physics research to interface many different kinds of transducers, and actuators to digital computers. A number of laboratories in the United States and Europe have established a standard interfacing system known as Camac, an acronym for Computer Aided Measurement and Control. It consists of a number of bins or crates, each of which will accept up to 24 modules containing instrumentation to be interfaced to the computer. These modules will each have one or more of the following functions:

> Accepting logical commands from a computer, Sending status information to a computer, Accepting numerical data from a computer, and/or Sending numerical data to a computer.

Camac replaces the great variety of input-output equipment found in various models of computers by a single nonproprietary design standardised both electrically and mechanically to ensure compatibility between modules supplied by different manufacturers.

At the rear of the crate, there is a dataway which provides power to the modules and also links them to the computer. It is designed to minimise the logic needed in a module and also to provide a large repertoire of operations for the module designer. The architecture of the dataway is not patterned on the input/output structure of any make of computer, and it is therefore necessary to interface it to the chosen computer, that is, to resolve the time and logic differences between the dataway and the host input/output system. Although this may seem to be merely a case of shifting the interfacing problem to a different part of the system, there are significant advantages. The interfacing task is performed just once for all the modules. The instruments and the computer are made independent and either may be changed or replaced with no effect on the other. Thus different combinations of modules, each combination representing a particular electronic interface between the computer and experimental apparatus, can be set up with no greater effort than placing the required modules in a crate and plugging them together and to the external

experiment, and several groups of modules, each handling a different experiment, can operate in parallel. Formerly a different electronic interface would have had to be constructed for each combination of modules. The price which must be paid for this flexibility is the addition of another unit variously called the interface, the branch driver, the Camac controller or the Camac processor.

#### The CAMAC Control Hierachy

In summary then, the Camac system provides the following control hierachy. Each module finds its home in a <u>crate</u> that secures it mechanically and provides its interface to the power supplies and the <u>dataway</u>. The dataway provides the means of interconnection between the modules and the <u>crate-controller</u> within one crate. Multicrate Camac systems are organised as one or more larger structural units called <u>branches</u> in which a branch highway provides the means of interconnection between crate controllers, in up to seven crates, and the <u>branch driver</u>. The branch driver is the interface between the Camac system and the computer.

#### The CAMAC LAM Concept

When a condition occurs in a module that requires attention by the computer the module generates a signal on its LAM (Look At Me) line. Each station in a crate has a LAM line assigned to it individually. Some of these may be directly connected the computer's interrupt system via a PIM (see the tables in appendix A4) to enable service routines to be invoked quickly and with low software overheads. All of the LAM lines in a crate are connected to a status line associated with the crate, which appears as the 8D (Branch Demand) bit in the status word that the computer can read from the Interface or branch driver. When the 8D bit is set, the computer may read the status of all 24 LAM lines in a crate and thus determine which modules require attention. Some modules may have more than one condition that can cause a LAM to be set. In this case the condition must be determined by specific test commands.

#### 6.2.2 The CAMAC System at the NIPR

#### Introduction.

The Camac system purchased by the NIPR\*\* includes modules to read analog signals from up to sixteen channels, to read digital data containing up to 36 bits, and to provide timing facilities to enable sampling of signals at programmable intervals.

The analog to digital converter (ADC) is used to sample an input voltage and convert it to a digital number which can be read by the computer.

The multiplexer is used in conjunction with the ADC to select one of sixteen input channels for conversion.

There are two clock/timers that can be used to initiate sampling operations or programs at programmable rates with a basic time unit of 0,1 milliseconds. Their LAM lines, which are set whenever a timer interval has expired, are connected to the computer's interrupt system thus enabling programs to be invoked at regular intervals.

There are two Input/Output registers which enable digital data to be read by the computer. Their LAM lines are also connected to the computer's interrupt system and are set by external equipment to indicate that there is new data available. This provides the facility for a program to lie dormant in the computer, thus freeing the processor for the use of other programs, until the experimental equipment requires attention.

The interface (branch driver) has an option crucial to the success of the feasibility study. This is the so-called Block Transfer Option which by, effecting series of CAMAC operations independently of the computer, allows data gathering to proceed in parallel with other processing.

\*\* The components of the CAMAC purchased by the NIPR are listed in Table Al.

Descriptions of the facilities and functions of each module may be found in appendix A5, in the manufacturer's manuals, and in a report on Camac programming to be published by the NIPR.

#### <u>Elock Transfer of Data</u>

The special features of the Varian BIC and PIM, the Camac ADC, multiplexer, and clock/timer modules are exploited by the Block Transfer Option of the Camac interface to allow data input to the computer with a minimum of CPU involvement in the data transfer process. The fundamantal function of the Block Transfer Option is to issue a specified Camac command a predetermined number of times. The way it is used in a typical multi-channel data sampling program is as follows :--

The program must initialize

- the BIC with the initial and final memory address of where it is to store the incoming data,

- (2) the multiplexer with the first channel to be sampled,

- (3) the clock/timer with the sample interval, and

- (4) the Block Transfer Option with the number of channels to be sampled and the Camac command to read data from the ADC.

The program then activates the block transfer and relinquishes control of the computer so that the CPU is free to be used by another program while the data transfer takes place in the following manner :

At the end of the sampling interval, the clock/timer generates a signal which actually begins the data transfer process. The ADC use this pulse to initiate the sampling of the signal on the first multiplexer channel, and its conversion to a digital value. At the end of the conversion, the ADC generates a pulse which signals the Block Transfer Option in the interface to issuera Camac read command to the ADC. The value converted by the ADC is passed to the BIC which stores it in the computer's memory without interrupting other processing. The read command also causes the ADC to pulse the multiplexer to cause it to switch to the next channel. When the switch has been completed the multiplexer pulses the ADC (as the timer did) causing it to begin a new sample and conversion. The cycle continues until the count which was set in the Block Transfer Option has been reached when an interrupt to the computer is generated. The interrupt processing routine initialises the BIC and Block Transfer for the next sample and processes the data in the required way.

The way this Block Transfer of data frees the CPU for processing other programs during the data acquisition cycle is illustrated in the timing chart in Figure 6.2.

From TO TI the CPU is initialising the data transfer function. From T1 to In, when the last data word has been read, the CPU is free. From T1 to T2 the clock is timing the sample interval. T2 is the end of the sample interval and the start of the data transfer. From T2 to T3 the ADC is converting the signal on the first data channel. From T3 to T4 the Block Transfer is issuing the first read command. At T4 the ADC receives the read command, and passes the data to the SIC. At T5 the ADC pulses the multiplexer. From T5 to T6 the multiplexer is switching channels. At T6 the multiplexer pulses the ADC and begins to second cycle. At In the Block Transfer Function signals the CPU that the required number of data values have been read.

#### Chapter 7

### Relevant Software

#### 7.1 The VORTEX Operating System.

The VORTEX operating system of the Varian 73 computer provides for multiprogramming for several foreground programs (i.e. those which reside simultaneously in memory and are processed according to priority) and one background program which has the lowest priority and is liable to be moved from memory to disk if foreground programs require additional space. Jobs that are not time-dependant are run in the background. The system also provides device-independent I/O facilities. Real-time processing is implemented by hardware interrupt controls and software task scheduling, of foreground programs. Tasks may be scheduled for execution by operator requests, other tasks, device interrupts or the completion of time intervals. Background processing operations, such as Fortran compilations or DAS MR assemblies, are under control of the job control processor, itself a VORTEX background task, and which is run whenever there is sufficient memory and no foreground program is waiting to run. Transfer of control between programs is effected by interrupts or by scheduling.

All tasks are scheduled, activated, and executed by the real-time executive (RTE) component of the operating system on a priority basis. The services that the RTE provides include :

Scheduling a task. Suspending a task. Resuming execution of a suspended task. Delaying the requesting task for a specified time. Aborting a task.

The VORTEX Input/Output Control (IOC) component processes all requests for I/O to be performed on peripheral devices thereby providing a common, device-independent I/O system.

The VORTEX system is generated from a collection of manufacturer supplied programs on magnetic tape thus tailoring the operating system, to the specific requirements of each user installation. User written programs, such as interrupt handlers, can be incorporated into the operating system during the system generation process. Each time new facilities such as new peripherals or new interrupt processing routines are required the system must be regenerated.

### 7.2 CAMAC Programming under VORTEX.

In a multiprogramming environment two problems arise in real-time applications using a system such as the Camac.

Firstly, programs must ensure that they do not interfere with other programs by simultaneously using non-shareable resources, Since VORTEX does not provide the means of allocating resources to a particular task and allowing tasks to queue for allocation is only found in operating systems on larger machines, user programs must provide these functions for themselves. To provide these facilities on the NIPR machine, a set of conventions has been drawn up and is described in appendix A6 and in a report on Camac programming to be published by the NIPR. Secondly, the handling of interrupts must be transparent to all tasks running under VORTEX (i.e. the tasks must not have to take account of interrupts for other tasks) and it must be done in such a way as not to delay or interfere with time-critical tasks. VORVEX provides for user written interrupt handlers to be incorporated into the operating system at system generation time. but, although this eases the problem of ensuring transparancy, the software overheads in scheduling the task were estimated to be too great. However, writing a non-standard interrupt handling program turned out to be a relatively simple problem. The actual details and an example program are given in appendix A7.

In summing, the three possible ways of handling the Camac units under VORTEX are :

- Incorporating a driver into the operating system This is too costly in overheads.

- (2) Incorporating a user-written interrupt handler routine -This is also too costly in overheads.

- (3) Writing a non-standard interrupt handler program invisible to and outside the VORTEX system.

- 25 -

The third possibility was the one chosen for implementation at the NIPR.

#### 7.3 Data Collection

The primary purpose of the Camac system is data acquisition and so the central function of the supporting software is that of data acquisition and storage. In each data acquisition program this is accomplished by 3 independent, cooperating processes. The first and main process, running as a VORTEX task, communicates with the user and controls the data acquisition process and the data storage process by providing blocks of storage in memory and by allowing the user to specify certain parameters. The data acquisition process is implemented as an interrupt routine that is invoked whenever the appropriate interrupt occurs; e.g. expiration of the timer interval or completion of a block transfer of data. This task runs invisibly to the VORTEX system and to all tasks running under VORTEX. The third process, called the writer, runs as a standard VORTEX task so that it can use the standard operating system I/O facilities for dumping data to disk or magnetic tape. This organisation is depicted in figure 7.1 below.

#### Figure 7.1 Data Collection System

VORTEX 11 CONTROL TASK experiment User Communication control Common INTERRUPT HANDLER Communication data input Data Acquisition Block via Camac WRITER TASK data storage Store data on tape or disk ſſ VORTEX

# The Verification of Data Spooling Capacity

#### 8.1 Data Transfer Rate

The rate at which data can be transferred to disk or magnetic tape is crucial to the success of the feasibility study. The first step, therefore, was to measure the actual maximum data rates that could be sustained by the disk and the tape as opposed to the theoretical values upon which the initial estimates of feasibility had been based. Account also had to be taken of the effect other programs could have on the data transfer rate.

To appreciate the results of the experiments which are summarised in table 8.1 below, some understanding of the way in which data transfer takes place is mecessary. Data transfers to disk, to tape and from the Camac take place under control of the BIC option of the Varian 73. In chapter 6 it was explained that when the BIC transfers a word of data to or from memory it inhibits processing of the CPU for one memory cycle. In table 8.1 the maximum effective rate at which data can be written to the disk is shown to be 35,95 words per millisecond. At this rate an average of one in 42,146 memory cycles are used by the BIC to transfer a word out of memory. For the magnetic tape, the maximum rate of data transfer is 9,30 words per millisecond, which corresponds to one in 162,920 memory cycles. In the worst possible case, with data being written out both to disk and to tabe at maximum rates and being read at 16 words per millisecond from the Camac system under Block Transfer, the total data rate of 61,25 words per millisecond is achieved which requires one in 24,73 memory cycles. Another program running simultaneously with the data transfers would therefore experience a drop in CPU speed of only 4,04%.

<u>Conclusions</u>: The maximum data rate that the disk will support, 35 words per millisecond, is well above the required maximum data sampling rate of 16 words per millisecond. The tape can support a maximum data sampling rate of 9 words per millisecond. At this rate, however, it requires all of available memory for buffers. With a reasonable buffer size of 1200 words the tape has a maximum data rate of 7 words per millisecond. This is well above the maximum rate expected from experiments other than EEG experiments. A buffer of 2000 would allow the data from an EEG experiment using 8 channels to be written to tape.

| Table 8. | 1 | Dis |

|----------|---|-----|

|----------|---|-----|

#### isk and Tape Data Rates

| Rate at which data is written to :<br>(in words per millisecond) |             |                   | Buffer | Size - | Number of | words         |

|------------------------------------------------------------------|-------------|-------------------|--------|--------|-----------|---------------|

|                                                                  |             |                   | 120    | 1200   | 2400      | 5760          |

| DISK                                                             | -           | ALONE             | 2,93   | 18 🎝   | 20,64     | 35,95         |

| DISK                                                             |             | WITH COPY PROGRAM | 1,18   | 9,31   | 15,60     | 25 <b>,65</b> |

| TAPE                                                             | <b>e</b> ., | ALONE             | 2,13   | 7,32   | 8,20      | 9,30          |

| TAPE                                                             | <b>6</b> 53 | WITH COPY PROGRAM | 2,13   | 7,32   | 8,20      | 9,29          |

Note : Data transfers to the disk in multiples of disk sectors which are blocks of 120 words so that, for efficient use of the disk, data should be in records that are multiples of 120 words. For ease in comparison between disk and tape timings, the buffer sizes for the tape were the same as for the disk.

The copy program simulates other user program activity requiring the disk.

# 8.2 The Effects of Conflict Between Programs for Access to the Disk

When data is transferred to disk, the disk read/write head is positioned to the correct track and it then waits until the correct sector appears beneath it before beginning the data transfer into sequential sectors. There are therefore two overheads and two potential bottlenecks :

- (1) The seek to the correct track, and

- (2) The search for the correct sector.

The second factor is inherent in rotating memories and is not affected the way the disk is used. However, the disk drive has only one head to serve both disks, thus, if more than one disk file is being accessed simultaneously, there will be competition for use of the head and in the worst case, the head will be moving continually from one file to the other. As a result, if, in a real-time experiment in which data is being logged to disk, other programs are also to access the disk, then the time for the read/write head to locate the data acquisition program's file and the data transfer time must be less than the rate at which data is being read by the Camac system.

The effect of competition for the disk head was measured by running a file copy program, which transferred a file from one part of the disk to another, simultaneously with a test program which wrote to the disk at maximum speed. The experiment was not the worst possible case, but represented a situation that would be commonly encountered in practice. The test program wrote across the entire disk, but the copying program used files located towards the middle of the disk surface rather than at either extreme.

#### 8.3 Effects of Conflicting Priorities

All data transfer is initiated by software and it was here that another possible bottleneck was identified. The interrupts for the disk have higher priorities than those for the tape and it appeared likely that when disk interrupts were being generated at a maximum rate that the processing of these interrupts and the scheduling of new disk data transfers could possibly delay the scheduling of data transfers to the tape. This effect was measured by copying one file to itself in blocks of 120 words, or 1 disk sector, while writing to tape at the maximum rate with a program of higher priority. <u>Conclusions</u> The results in table 8.1 above show that the effect of heavy disk usage on the tape data rate is negligible.

#### 8.4 Comparison of Actual with Theoretical Timing Calculations

The actual times measured for writing to the disk (in stand alone mode) are a little less than those calculated by adding the maximum access time to the product of the data transfer rate and the buffer size. The tape writing times are a little longer than the calculated times, and the measured start-up time at 130 milliseconds is significantly longer than the theoretical 18 milliseconds.

#### 8.5 Summary

To summarise, the data handling capacities of the disk and the magnetic tape units are more than adequate for the maximum requirements of the experiments presently planned at the NIPR providing adequate buffers are used.

#### Chapter 9

# Verification of the Time-Sharing Capabilities

#### of the System

#### 9.1 Introduction

Experience with the system and experimental measurements have shown that time-sharing a mini-computer in the NIPR environment is feasible. Two real-time data acquisition programs have been written and used in live psychological experiments, simultaneously with program development at two other terminals with no interference of real-time programs by non-real-time programs. The only degradation experienced by the non-real-time programs was that imposed by the limitations of main memory space. Timing measurements were made with programs run both alone and in contrived bottlenecks and, with two caveats, have proved that the system provides adequate time-sharing facilities for the NIPR.

#### 9.2 Terminology

Terms which may require some explanation and are used throughout the report are defined in the glossary in appendix A8. Specifically in this chapter from section 9.3 onwards the term PROJECT is used to refer to a "live", psychological experiment where the computer was used as a tool, and EXPERIMENT refers to the case where the computing system itself was the subject of an experiment in the feasibility study. Also, NORMAL MODE is used to describe the mode of data acquisition from the Camac unit using an explicit series of Camac I/O instructions in place of Block Transfer.

#### 9.3 Experience with the System

Two programs were used in live projects for real-time data acquisition : (a) A program for the Personality and Temperament Division sampled one channel of data from an electrocardiogram at 1 millisecond intervals. Its main memory requirements totalled 8k with 1k data beffers. This program was run continuously for about 10 weeks from April to June 1975 and thereafter once or twice weekly. (b) A program, for the Neuropsychology Division, sampled one channel of electro-encephalographic data at 1 millisecond intervals and required 5k of main memory with buffers of 2k. This program was in continuous use over a period of two and a half weeks.

During the time that a real-time data acquisition program was running, normal program development, i.e. file editing, assemblies, testing in the background, etc., continued at one and sometimes two other terminals. There was no instance of a real-time program being affected by a nonreal-time program during this period. Non-real-time programs experienced some degradation because of the small amount of main memory available for their use. This was particularly acute when the ECG program was running because there was then insufficient room for the DASMR assembler. Neither the EEG nor ECG programs left enough space for the Fortran compiler.

The reason the ECG program is 3k larger than the EEG program despite substantially smaller buffers is that it had one subroutine in Fortran which required system supporting subroutines accupying 3-4k. Further, these subroutines are not reentrant. This points to a limitation, namely, time-sharing programs should not be written in Fortran owing to its large demands on main memory or, alternatively, if the ease of programming provided by Fortran is important, then 24k of memory is inadequate and at least 32k is necessary.

The EEG and ECG programs could not be used simultaneously in a live experiment because both require the ADC. This could be remedied by the purchase of a second ADC. This illustrates an important advantage of the Camac system, i.e. additional modules for multiplexing data acquisition can be installed at little extra expense and with no additional interfacing or control requirements.

The most important conclusion from these operations is that the hardware and software are reliable and secure enough for development to proceed in parallell with real-time experiments. The provision of an interactive psychological test-presentation facility has involved a large amount of program development, all of which was carried out in parallel with either the real-time projects or other development. Development would have been considerably delayed if this work had had to wait its turn in the job queue.

#### 9.4 Experiments for Timing Interrupt-Driven Transfers of Control

### 9.4.1 <u>Introduction and Background to the Timing Exper</u>iments

Experiments were also carried out to extend the experience provided by actual processing. Measurements of timing parameters were made for both modes of real-time data acquisition through the Camac system, and also for some of the Real Time Executive services of the VORTEX operating system. The procedures followed and the measurements made are described in the following sections in enough detail to allow the experiments to be repeated. The non-technical reader may skip to a summary of the results in section 9.4.9.

At the beginning of the experiments several problems were encountered which, in the end, turned out to be more of theoretical than practical importance.

- (a) Both the Varian and the Camac Timers have a resolution of 0,1 milliseconds and, as this is the order of the discrimination required in the timing measurement, rounding errors are large. However, definite conclusions could still be drawn from the results.

- (b) Timing measurements were made by adding instructions for reading a clock to existing interrupt processing routines. This modified the behaviour of these routines, but not so as to prevent useful results being obtained.

- (c) The critical parameter was the delay in initiating an interrupt servicing routine following an interrupt. There is no way of measuring this time directly by software, but is possible to infer it reasonably accurately from other measurements.

#### 9.4.2 The Data Acquisition Process

To understand the experiments it is necessary to describe the data acquisition process in more detail than is chapter 7.

The Camac system is used for data acquisition in one of two modes. When Block transfer is used, data from Camac modules is transferred to the computer under control of a BIC. Otherwise, in Normal Mode, the data is read in with a series of Camac I/O commands issued under program control. A Camac timer times the sampling process in both cases but the timing signal is used differently.

- 33 -

#### Block Transfer

With the Block Transfer of data, the pulse from the clock starts a process consisting of a number of cycles of acquisition, conversion and transfer to the computer memory, independently of the CPU, and only when all the data has been transferred is an interrupt generated. The interrupt servicing routine reinitializes the BIC and Block Transfer and may do (a small amount of) processing on the data.

If data is not to be lost, it is necessary that the data conversion and transmission time, Tc, plus the delay in servicing the interrupt, Td, plus the interrupt service time, Ti, be lass than the sample interval Ts. This is illustrated in figure 9.1 below. Because the digitising is started by the clock and carried out independently of the computer the variation in the sampling interval depends only on the accuracy of the clock. The advantage of Block Transfer is that the CPU has the interval To available for processing other programs.

- Ts : Sample interval.

- To : Data conversion and transmission time for a channels.

- Td : Delay in initiating the interrupt servicing routine.

- Ti : Interrupt servicing time.

- A\_ : Clock Pulse; commencement of data conversion process.

- B\_ : BIC complete interrupt; end of data transmission.

- C<sub>n</sub> : Control passed to interrupt servicing routine.

- D\_ : Control returned to interrupted program.

- Notes : Ts is constant within the order of accuracy of the Camac Timer. To does not very much (see section 9.4.6) and is, for 16-channels, 0,55 milliseconds.

- Td is unpredictable for it depends on the length of time other programs hold back interrupts while they carry out non-interruptible operations.

- Ti depends on the lengths of the servicing routine and the operational cycle time of the CPU: The latter may vary according to the amount of cycle stealing used for data transfer. To represents the time the data acquisition program required exclusive use of the CPU.

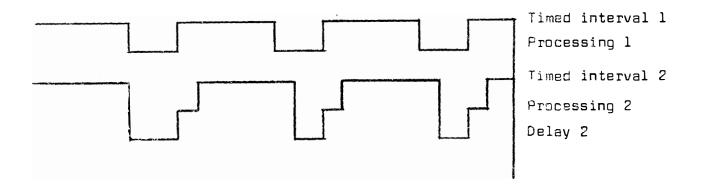

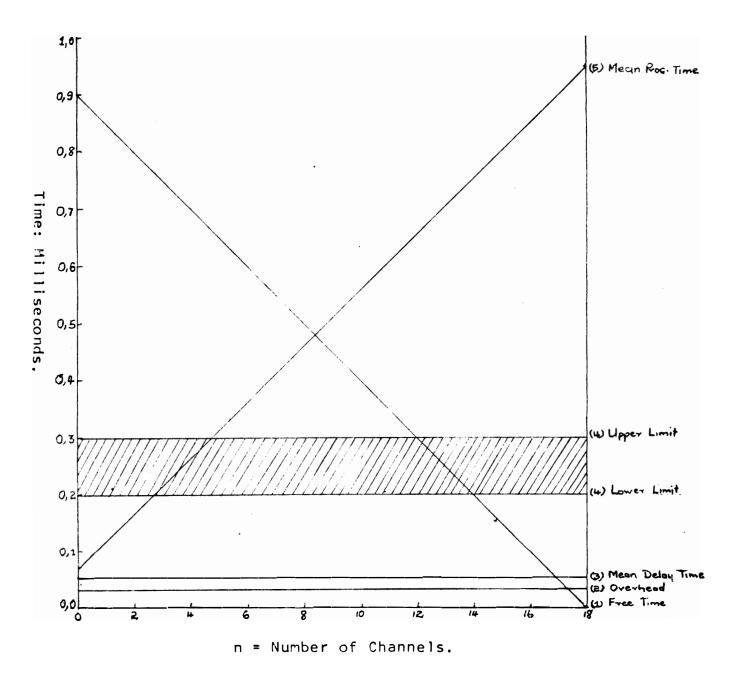

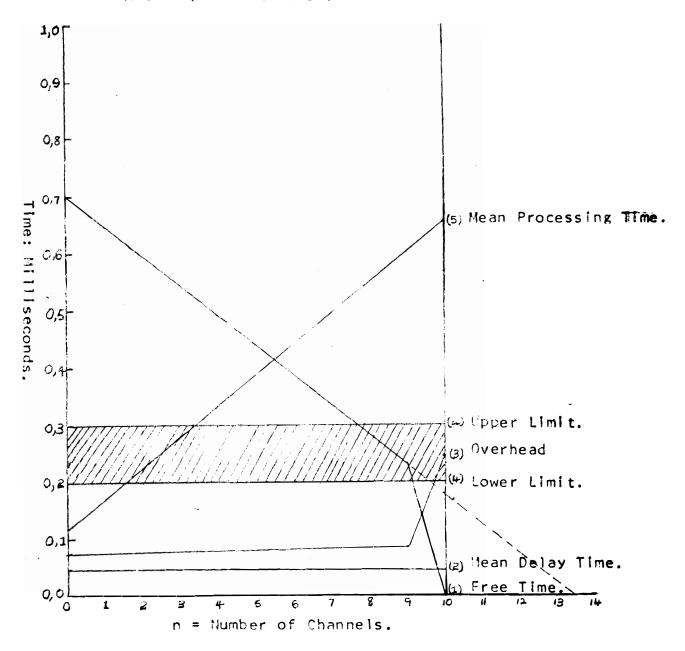

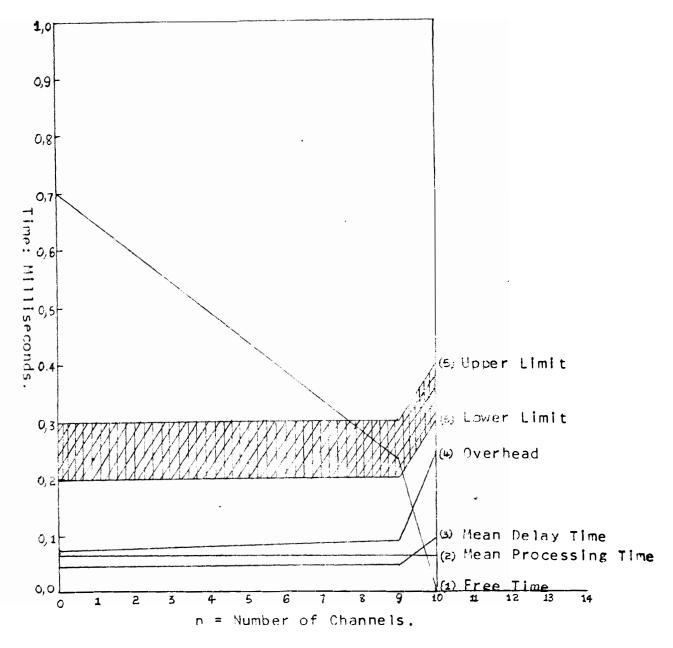

#### Normal Mode